Open-source project from Xilinx® that enables high-level control of Versal debug IP running in hardware

Project description

🐍 ChipScoPy README

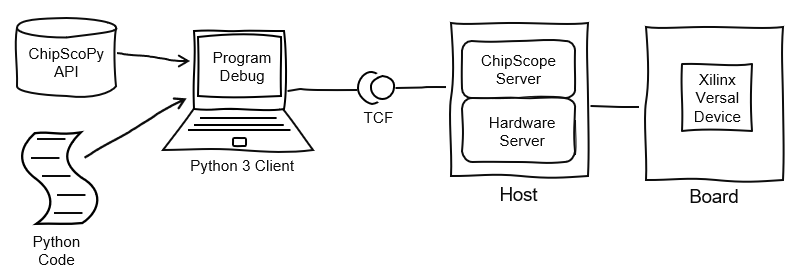

ChipScoPy is an open-source project from Xilinx® that enables high-level control of Versal debug IP running in hardware. Using a simple Python API, developers can control and communicate with ChipScope® debug IP such as the Integrated Logic Analyzer (ILA), Virtual IO (VIO), device memory access, and more.

ChipScoPy communicates with Versal devices. It does not work with older devices such as Ultrascale+ and 7-Series devices.

We recommend using Python 3.8, 3.9, 3.10, or 3.11 with ChipScoPy.

Copyright (C) 2021-2022, Xilinx, Inc.

Copyright (C) 2022-2024, Advanced Micro Devices, Inc.

Licensed under the Apache License, Version 2.0 (the "License"); you may not use this file except in compliance with the License. You may obtain a copy of the License at

http://www.apache.org/licenses/LICENSE-2.0

Unless required by applicable law or agreed to in writing, software distributed under the License is distributed on an "AS IS" BASIS, WITHOUT WARRANTIES OR CONDITIONS OF ANY KIND, either express or implied. See the License for the specific language governing permissions and limitations under the License.

Project details

Release history Release notifications | RSS feed

Download files

Download the file for your platform. If you're not sure which to choose, learn more about installing packages.

Source Distribution

Built Distribution

Filter files by name, interpreter, ABI, and platform.

If you're not sure about the file name format, learn more about wheel file names.

Copy a direct link to the current filters

File details

Details for the file chipscopy-2024.1.dev1715183651.tar.gz.

File metadata

- Download URL: chipscopy-2024.1.dev1715183651.tar.gz

- Upload date:

- Size: 8.9 MB

- Tags: Source

- Uploaded using Trusted Publishing? No

- Uploaded via: poetry/1.6.1 CPython/3.10.13 Linux/5.4.0-173-generic

File hashes

| Algorithm | Hash digest | |

|---|---|---|

| SHA256 |

845f202abde1e4d00623487e5fb209e454f47769a97dee7804f24e03d6a7f144

|

|

| MD5 |

d4c2e4aa6f230d45ce8e2ab2d2e2fff9

|

|

| BLAKE2b-256 |

e6eadcbd7d302dd9162d450640c9986bc9d4429618f5ee0b4074afd963a94852

|

File details

Details for the file chipscopy-2024.1.dev1715183651-py3-none-any.whl.

File metadata

- Download URL: chipscopy-2024.1.dev1715183651-py3-none-any.whl

- Upload date:

- Size: 9.1 MB

- Tags: Python 3

- Uploaded using Trusted Publishing? No

- Uploaded via: poetry/1.6.1 CPython/3.10.13 Linux/5.4.0-173-generic

File hashes

| Algorithm | Hash digest | |

|---|---|---|

| SHA256 |

8b5b4755332da5ce5397e1a067851e0c126cabe4bcda5cd3787199c3da99b46e

|

|

| MD5 |

0a7ea4300b25600e8db4df46bf18d5f2

|

|

| BLAKE2b-256 |

0cd5559e0a2a384acd1364461b49043c6757ef14f0df4cb321e90aa11a9c439e

|