Interactive Digital Logic Simulator

Project description

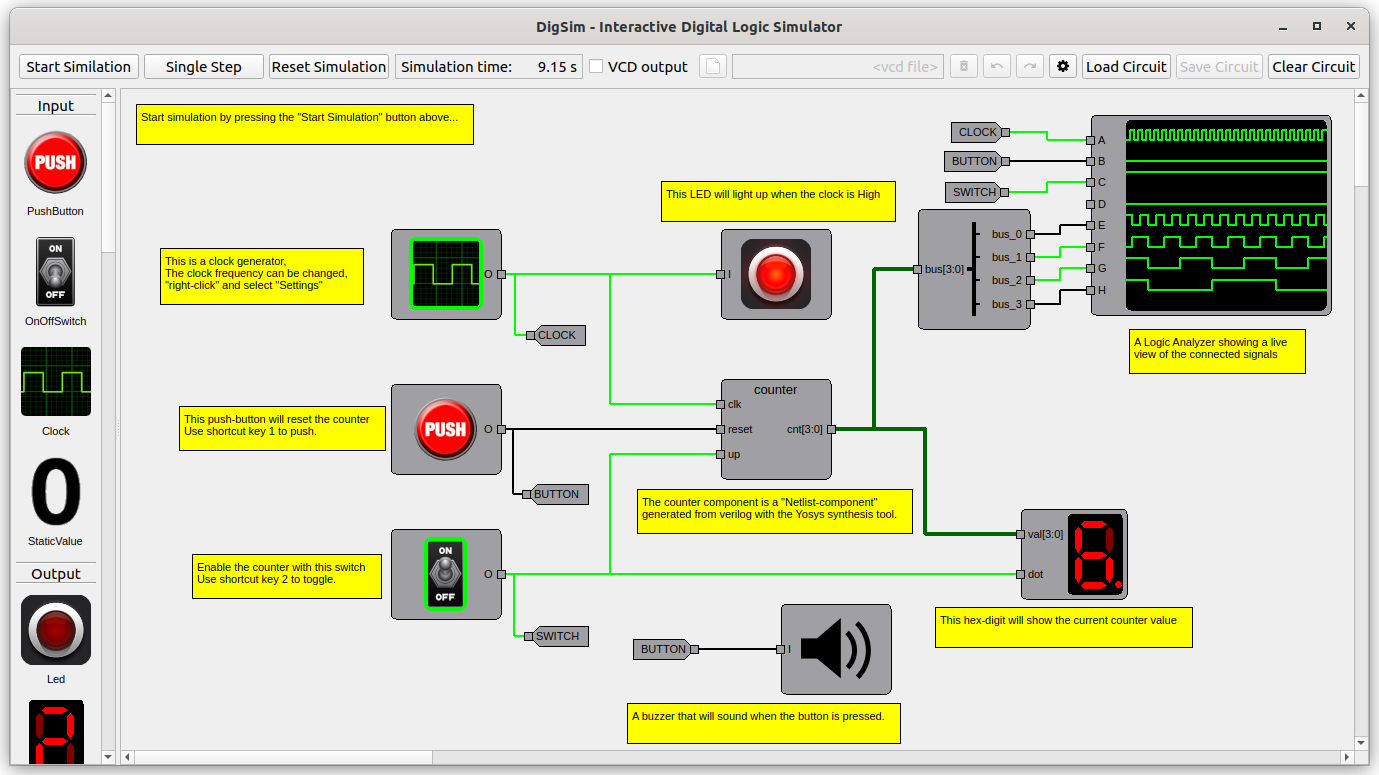

DigSim - Interactive Digital Logic Simulator

Introduction

DigSim is a python based framework for digital circuit simulation. The main purpose of the software is to, in an educational way, play around with digital logic (simple gates and verilog designs).

When working with block design in Verilog/VHDL the simulation tools are normally fed with test stimuli (a very non-interactive way of working...) A block design can be synthesized and tested on an FPGA (where there are possibilities for interactivity if buttons and LED/Hex digits are available), but that often has a great cost in time (and sometimes money) leading to long turnaround time.

I started developing DigSim to make it easy to implement and visualize the functionality of simple verlog modules. During development I tried to synthesize larger verilog designs, such as the classic 6502 CPU, and even if it is slower than many other simulators it is not entirely useless.

Features

- Create and simulate a circuit using python code

- Create and simulate a circuit interactively using the GUI

- Create new components using synthesized verilog code

- Save simulation results in VCD files, which can be opened in for example GTKWave.

Quickstart

Install from PyPi (Option 1)

pip3 install digsim-logic-simulator

Install from GitHub (Option 2)

> git clone https://github.com/freand76/digsim.git

> cd digsim

> python3 -m pip install .

Start Interactive GUI

Prerequisites: Install by using Option 1 or Option 2 above.

> python3 -m digsim.app

or

> digsim-logic-simulator

Start using uv

Prerequisites: Download and install uv

> uvx digsim-logic-simulator

Note: Ubuntu

If your Ubuntu installation gives the folloing error message:

qt.qpa.plugin: Could not load the Qt platform plugin "xcb" in "" even though it was found. This application failed to start because no Qt platform plugin could be initialized. Reinstalling the application may fix this problem.

Available platform plugins are: vnc, wayland, wayland-egl, eglfs, offscreen, xcb, minimal, linuxfb, vkkhrdisplay, minimalegl.

Then the following package must be installed:

> apt install libxcb-cursor0

Start with example circuit (example circuits are available in the github repository)

> python3 -m digsim.app --load example_circuits/counter_yosys_netlist.circuit

Run example (examples are available in the github repository)

> python3 examples/example_sr.py

Look at waveforms

> python3 examples/example_sr.py

> gtkwave sr.vcd

Examples of writing pytest/python test benches for synthesized verilog code

> pytest examples/pytest_tb

Yosys synthesis helper tool

> python3 -m digsim.synth synth -i <verilog file 1> <optional verilog file 2> -o <output_file.json> -t <verilog top_module>

Documentation

Documentation on GitHub

Star History

Project details

Release history Release notifications | RSS feed

Download files

Download the file for your platform. If you're not sure which to choose, learn more about installing packages.

Source Distribution

Built Distribution

Filter files by name, interpreter, ABI, and platform.

If you're not sure about the file name format, learn more about wheel file names.

Copy a direct link to the current filters

File details

Details for the file digsim_logic_simulator-1.0.0.tar.gz.

File metadata

- Download URL: digsim_logic_simulator-1.0.0.tar.gz

- Upload date:

- Size: 253.0 kB

- Tags: Source

- Uploaded using Trusted Publishing? No

- Uploaded via: twine/6.1.0 CPython/3.12.3

File hashes

| Algorithm | Hash digest | |

|---|---|---|

| SHA256 |

b667fd3166d5031d2a43d330f13f494f428b23097b565ffb8a5b58f3784dcad2

|

|

| MD5 |

867d0cb89e2f0bc4610d08f5b2101c5a

|

|

| BLAKE2b-256 |

d549a35d89ab615ba955d7684075f227416800efcb308693cf39e717b5083774

|

File details

Details for the file digsim_logic_simulator-1.0.0-py3-none-any.whl.

File metadata

- Download URL: digsim_logic_simulator-1.0.0-py3-none-any.whl

- Upload date:

- Size: 287.8 kB

- Tags: Python 3

- Uploaded using Trusted Publishing? No

- Uploaded via: twine/6.1.0 CPython/3.12.3

File hashes

| Algorithm | Hash digest | |

|---|---|---|

| SHA256 |

dec1695eb42227e6bf31fc92f8d677bf2daab59d8c6d0d2ac8eebae3a73dc20b

|

|

| MD5 |

735d00eeca716ef1e594ce226b38606a

|

|

| BLAKE2b-256 |

d599aae9f43f5f4daacc601ce83e2e9968a8bfc3db64e7f253a5f37addaaaa07

|